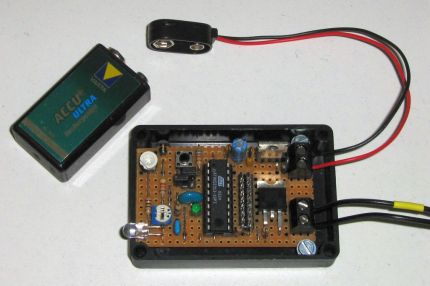

Eine Digitalkamera der unteren Preisklasse bietet in der Regel keine Möglichkeit zum Anschluss externer Blitzgeräte. Daher wurde dieser Zweitblitzauslöser gebaut, welcher den Blitz der Digitalkamera detektiert und dann ein externes Blitzgerät auslöst. (April 2010)

Die Blitzerkennung erfolgt mit einem Fototransistor mit nachgeschaltetem Hochpass zur Unterdrückung von langsamen Helligkeitsänderungen. Da viele Digitalkameras vor dem der eigentlichen Aufnahme dienenden Hauptblitz noch einen oder mehrere Vorblitze abgeben, darf die Auslösung erst nach einer bestimmten Anzahl von empfangenen Blitzen erfolgen. Dies wird mit einem entsprechend programmierten Mikrocontroller vom Typ AT90S2313 erreicht, welcher die Blitze zählt und bei einer einstellbaren Anzahl von Blitzen das angeschlossene Blitzgerät auslöst. Die Anzahl der zur Auslösung erforderlichen Blitze ist im Bereich von 1 bis 4 einstellbar. Zusätzlich kann eine Wartezeit von 0 bis 255 ms eingestellt werden, um welche die Auslösung verzögert wird.

Der Mikrocontroller wurde in Assemblersprache programmiert. Der Einfachheit halber wurde auf die Verwendung von Interrupts und Timern verzichtet. Nach dem Reset wird zunächst die Hardware initialisiert. Danach wird die über die Jumper eingestellte Blitzanzahl und Wartezeit eingelesen. Dann wird auf den ersten Blitz gewartet. Wurde ein Blitz registriert, wird die Kontroll-LED eingeschaltet, der Blitzzähler inkrementiert und auf den nächsten Blitz gewartet, falls die eingestellte Blitzanzahl noch nicht erreicht ist. Wenn die Blitzanzahl erreicht ist, wird für die eingestellte Wartezeit gewartet und danach der Zweitblitz-Ausgang für 10 ms aktiviert. Danach wird die Kontroll-LED abgeschaltet und das Programm fährt mit dem Einlesen von Blitzanzahl und Wartezeit fort.

; Zweitblitzauslöser ; von Nils Hintze ; Taktfrequenz 8 MHz ; Pinbelegung: ; PB0..7: Wartezeit-Einstellung, binär, LOW-aktiv ; PD0..1: Blitzanzahl-Einstellung, binär, LOW-aktiv ; PD3: Ausgang für Kontroll-LED, HIGH-aktiv ; PD5: Eingang für Blitz-Erkennung, LOW-aktiv ; PD6: Ausgang für Zweitblitz-Auslösung, HIGH-aktiv .include "2313def.inc" .def temp = r16 .def temp1 = r17 .def temp2 = r18 .def wcount = r19 .def wtime = r20 .org 0 reset: ldi temp, RAMEND ; Stackpointer initialisieren out SPL, temp ; ldi temp, 0b00000000 ; Portpins an PORTB sind alle Eingänge out DDRB, temp ; ldi temp, 0b11111111 ; Ziehwiderstände für Eingänge aktivieren out PORTB, temp ; ldi temp, 0b1001000 ; PD0..1 und PD5 sind Eingänge, PD3 und PD6 sind Ausgänge out DDRD, temp ; ldi temp, 0b0010111 ; Ziehwiderstände für Eingänge aktivieren, ausg. Blitzeingang out PORTD, temp ; rcall w100ms ; 100 ms warten main: in temp, PIND ; Blitzanzahl einlesen com temp ; andi temp, 0x03 ; inc temp ; mov wcount, temp ; in temp, PINB ; Wartezeit einlesen com temp ; mov wtime, temp ; clr temp ; Blitzzähler löschen main1: sbic PIND, PD5 ; Warten bis Blitz erkannt rjmp main1 ; sbi PORTD, PD3 ; Kontroll-LED einschalten inc temp ; Blitzzähler inkrementieren cp temp, wcount ; Wenn Blitzanzahl erreicht zur Wartezeit breq wait ; rcall w1ms ; 1 ms warten main2: sbis PIND, PD5 ; Warten bis Blitzsignal wieder normal rjmp main2 ; rcall w1ms ; 1 ms warten rjmp main1 ; Auf nächsten Blitz warten wait: clr temp ; Wartezeitzähler löschen wait1: cp temp, wtime ; Wenn Wartezeit erreicht zur Blitzauslösung breq flash ; inc temp ; Wartezeitzähler erhöhen rcall w1ms ; 1 ms warten rjmp wait1 ; Weiter warten flash: sbi PORTD, PD6 ; Ausgang einschalten rcall w10ms ; 10 ms warten cbi PORTD, PD6 ; Ausgang ausschalten rcall w100ms ; 100 ms warten cbi PORTD, PD3 ; Kontroll-LED ausschalten rjmp main ; Alles auf Anfang! ; Warteschleife 8000 Zyklen mit rcall und ret, 1 ms bei 8 MHz w1ms: push temp push temp1 ldi temp, 14 w1msa: ldi temp1, 189 w1msb: dec temp1 brne w1msb dec temp brne w1msa nop nop nop nop nop pop temp1 pop temp ret ; Warteschleife 80000 Zyklen mit rcall und ret, 10 ms bei 8 MHz w10ms: push temp push temp1 ldi temp, 124 w10msa: ldi temp1, 214 w10msb: dec temp1 brne w10msb dec temp brne w10msa nop nop nop nop nop pop temp1 pop temp ret ; Warteschleife 800000 Zyklen mit rcall und ret, 100 ms bei 8 MHz w100ms: push temp push temp1 push temp2 ldi temp, 20 w100msa:ldi temp1, 66 w100msb:ldi temp2, 201 w100msc:dec temp2 brne w100msc dec temp1 brne w100msb dec temp brne w100msa nop pop temp2 pop temp1 pop temp ret

Quelltext: zweitblitz.asm

Die Intel-HEX-Datei für den AT90S2313 bzw. ATtiny2313 kann hier heruntergeladen werden: zweitblitz.hex.